# 三次元集積のためのインダクタ対 による無線インタコネクション

Wireless Interconnection Using Inductor Pair for 3D Integration

#### 岩田 穆

bstract

集積回路では素子の微細化による高集積化と高速化が進み,大量情報の高速な処理が可能となっているが,一層の情 報処理量の向上、高機能化の要求に対応するために複数チップの積層実装及び三次元集積技術の開発が活発になってい る. 従来, 積層チップ間にはボンディングワイヤ, 貫通ビア, バンプなど有線による情報転送が用いられてきたが, 高 速性、製造コスト、信頼性などの課題を抱えている。本稿では、インダクタ対による無線インタコネクト技術の原理、 構成法,性能について述べ,更に無線インタコネクトを用いた三次元実装や三次元集積の可能性と課題についても述べる. キーワード:電磁結合, 高速データ転送, チップ間通信, チップ積層

# 1. まえがき

20世紀の後半から、シリコン集積同路技術はムーア の法則に沿って集積規模が2年で2倍の凍度で発展して きた. デバイスの超微細加工技術とアーキテクチャ・回 路技術の進歩により、集積規模は拡大してきた. CMOS デバイスや配線の微細化は半導体技術のロードマップに 沿って,65nm,45nmの世代へと進展していく.しかし, 21世紀に入って微細化によるチップの集積規模の増加 は、製造コストと設計コストの増加のため飽和の傾向が 見えている.

集積規模の増加に伴って、デバイス微細化による回路 の動作速度の向上に対して、配線の遅延時間が動作速度 を制限するようになった. 特にチップサイズの増加によ り配線が長くなるので、高速な配線が重要になる.シス テム規模の増加,機能の複雑化に対応して,複数チップ の積層が使われるようになった. システムインパッケー ジ(SIP)と呼ばれる実装技術である. この技術ではチッ プ間接続をボンディングワイヤなどの後処理工程で実現 するので,性能,信頼性などが課題となっている.一方, チップ間接続をウェーハ製造工程に組み込んだ三次元集 積技術の開発が活発になっている<sup>(1)</sup>. 三次元貫通ビアを 形成したチップを積層してバンプなどで電気的に接続す るなど各種の構成があるが、従来からの課題すなわち、 製造コスト, 歩留り、KGD(Known Good Die) (用語), 放熱, 信頼性の問題を抱えている.このように、三次元集積で チップ間のインタコネクト技術が最も重要な課題になっ

高機能化も重要であり、イメージセンサ、A-D変換器、 マイクロプロセッサ,メモリなどを各チップに作製して, それらを三次元集積することにより, 人間の視覚機能に 迫ろうとする研究も進められている<sup>(2)</sup>.

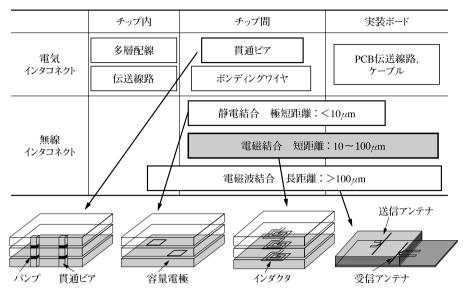

各種のチップ間インタコネクションを図1に示す. 最近, 注目されている無線インタコネクトでは、静電結 合、電磁結合、電磁波結合の3種類が提案されてい る(3)~(5). 静電結合は表面に電極を形成したチップを対 向接合して,チップ間絶縁層を挟んで形成したキャパシ タで結合する方法である. 3 チップ以上の三次元集積 にはチップ貫通ビアが必要である.これに対して、電磁 結合は各チップに形成したインダクタでマイクロトラン スを形成して磁界で結合させる方法である. インダクタ サイズの 1/2 程度の距離以下で必要な磁気結合係数が 得られるので、貫通ビアなしで三次元集積に適用できる. 電磁波結合はチップに形成したアンテナを用いてギガヘ ルツ以上の電磁波を伝搬させるので、100μm 以上の比 較的長距離のチップ間インタコネクションに適する.

岩田 移 正員:フェロー 広島大学大学院先端物質科学研究科半導体集積科学 専攻

E-mail iwa@dsl.hiroshima-u.ac.jp

Atsushi IWATA, Fellow (Graduate School of Advanced Sciences of Matter, Hiroshima University, Higashihiroshima-shi, 739-8530 Japan). 電子情報通信学会誌 Vol.90 No.10 pp.864-870 2007 年 10 月

図1 各種チップ間インタコネクション技術

# 2. インダクタ対による無線インタコネクション

# 2.1 原理

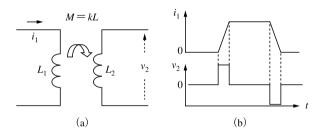

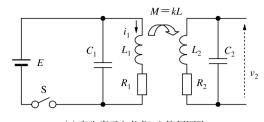

インダクタ対の電磁結合による無線インタコネクションの原理を図 2 (a) で説明する。インダクタに電流  $i_1$  を流す。電流が流れるとその周りにアンペアの法則により磁力線が発生する。磁力線の総和が磁束  $\mathbf{\Phi}_1$  であり,磁束と電流には  $\mathbf{\Phi}_1 = \mathbf{L}_1 i_1$  の比例関係があり,比例係数がインダクタンス  $\mathbf{L}$  である。大きな磁束を得るために導線を多数回巻いたコイルが用いられる。二次側のインダクタ  $\mathbf{L}_2$  を  $\mathbf{\Phi}_1$  の中に置くと, $\mathbf{L}_2$  を通過する磁束を  $\mathbf{\Phi}_2$  とすると, $\mathbf{\Phi}_2/\mathbf{\Phi}_1$  がインダクタ対の結合係数  $\mathbf{k}$  である。 $\mathbf{L}_2$  の両端には式(1)に示すように電磁誘導の法則により一次側の電流  $i_1$  の微分が誘導電圧  $v_2$  として発生する。

$$v_2 = \frac{d\Phi_2}{dt} = k \frac{d\Phi_1}{dt} = kL_1 \frac{di_1}{dt}$$

(1)

#### ■ 用 語 解 説

KGD (Known Good Die) 集積回路の製造工程では直径 20 あるいは 30cm のシリコンウェーハ上に 1,000 個程度のチップが製造されるが、その中で正常に動作するチップ (ダイとも呼ばれる)を選別すること. 現在はウェーハ上の各チップにプローブを接触させて、 LSI テスタを使って動作させて選別している.

RZ 方式 Return to Zero の略で、2 進ディジタル信号 "1"、"0"を通信するときに、1 データ区間内に必ず"0"に戻すようにするパルス波形を使う方式。データのタイミング情報も同時に送ることができる。一方、NRZ (Non Return to Zero) 方式では"0"に戻さない波形を使う.

図2 理想インダクタ対と応答特性 インダクタ対は入力電流の微分を電圧として出力するパルストランスである.

例えば $i_1$  が理想的な方形パルスの場合の $v_2$  の波形を図 2 (b) に示す。インダクタ対はパルスの遷移を伝える機能であり、パルストランスとも呼ばれる。

k は大きい方が好ましいが、後述するように信号伝送する場合は k>0.1、また、電力伝送する場合はk>0.5 が必要である.

## 2.2 集積化インダクタ

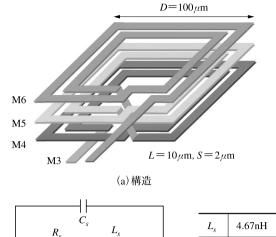

図3 集積化スパイラルインダクタ 集積回路の多層配線を 使ってインダクタが実現される. 電磁界解析で S パラメータを求 め, 等価回路で近似すると回路設計に使いやすい.

損を示し、 $R_{Si}$ はシリコン基板の導電性による渦電流損 を表す、結合係数 k とインダクタ間距離 d の関係を電 磁界解析で求めると、k>0.1 とするには d は外形の 1/2 以下にする必要がある.

#### 2.3 情報伝送回路

寄生素子を考慮したインダクタ対の等価回路とインダ クタを駆動するスイッチSの制御信号と $i_1, v_2$ の波形を 図 4 に示す。 $R_1$  はインダクタの直列抵抗とスイッチの オン抵抗の和である。k<1 の場合 $i_1,v_2$  の解析式は式 (2), 式(3) のようになる.

$$i_{1} = \frac{E}{R_{1}} \left[ 1 - e^{-\frac{t}{L_{1}/R_{1}}} \right]$$

(2)

$$v_{2} = -\frac{M}{C_{2}L_{2}}e^{-\frac{R_{1}}{2L_{2}}}\left\{\cos\left(\omega t\right) - \frac{R_{2}}{2L_{2}\omega}\sin\left(\omega t\right)\right\} \times i_{2}$$

(3)

受信信号は減衰振動波形となり、その振動周波数はイ ンダクタ対の自己共振周波数で定まる.

(a) 寄生素子を考慮した等価回路

図 4 寄生素子を考慮したインダクタ対の等価回路と応答波形 インダクタ対の寄生容量,寄生抵抗を考慮すると応答波形は減衰 振動になり、振動周波数はインダクタ対の共振周波数で決まる.

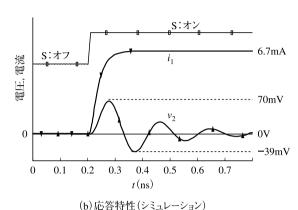

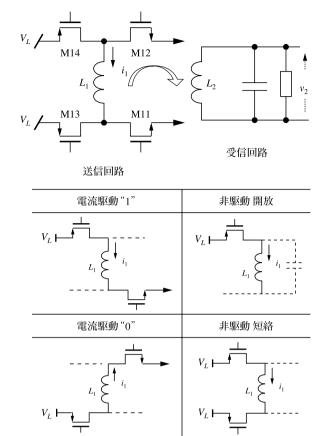

#### 2.4 送信電流駆動方式

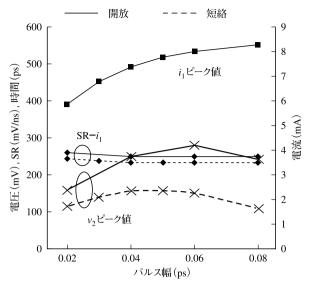

一般的なインダクタ駆動送信回路を図5に示す。イ ンダクタの電流の向きが単方向か双方向か、また、電流 非駆動時にインダクタが開放か短絡かという選択肢があ る. 受信信号のピーク値などの駆動パルス幅依存性をシ ミュレーションした結果を図6に示す.

パルス幅  $t_{PW}$  を自己共振周期  $(1/f_{self})$  の 1/2 程度にす ると、電流パルスの立ち上がりと立ち下がりによる応答 が重畳されて受信電圧振幅が最大になる. また, 非駆動 時は開放にした方が $v_2$ の振幅を2倍程度大きくできる ので、受信感度を一定とすると、インダクタの駆動電流 を減らし、消費電力を低減できる. また、インダクタン ス値依存性を調べると、これが小さいほど電流のスルー レートが上がり v2 が大きくなるが、電磁誘導の効果が 減る. したがって、 v2 を最大にするには最適なインダ クタンス値が存在する.

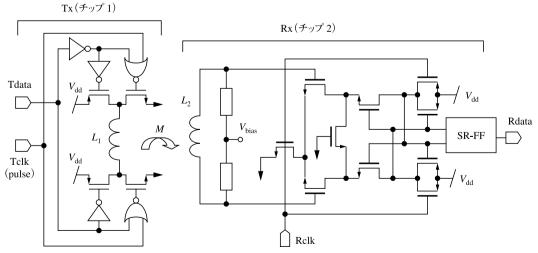

### 2.5 同期送受信回路

同期送受信回路を図7に示す。送信回路には両極性 電流駆動、受信回路には差動信号同期受信方式を用いて いる(7),(8). 送信回路は適当なパルス幅で駆動する RZ方 式(用語)であり、受信回路は同期クロックで動作するラッ チコンパレータを用いている。 コンパレータを低電力で 動作させることが可能であるが、受信電圧の減衰振動の 極性を正しく検出するには、検出タイミングマージンを 共振周期の1/2より十分小さくする必要がある。インダ クタを小さくすると自己共振周波数は高くなり, 受信同

図5 一般的なインダクタ駆動送信回路 送信側インダクタの駆動回路には種々の方式が考えられる.電流の向きは双方向か単方向か,また,電流のパルス幅はどう決めるか,非駆動時にインダクタを短絡するか開放するかなどがある.

期クロックのタイミングマージンが減少するので、高速化の限界となる.

同期多重伝送による多チャネルシステムが開発されている. データ 64ch に対して 1ch のクロック用インダク

図 6 駆動電流と受信電圧のパルス幅依存性 出力電圧振幅が最大になるパルス幅の最適値がある。非駆動時開放の方が短絡に比べて電圧振幅が1.5 倍程度大きくなる。 $SR-i_1$  は $i_1$  のスルーレート。

タ対を用いて、1,024ch 多重を実現している。多数のインダクタを高密度に配置するためにはクロストークの抑圧が必要である。このために、隣接する4個のインダクタを四相のクロックで駆動する方法(四相 TDMA:Time-Division Multiple Access)が提案されている<sup>(8)</sup>。

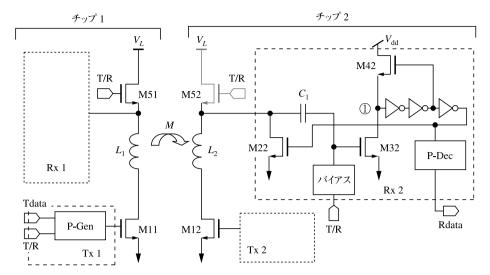

#### 2.6 非同期送受信回路

図8に非同期送受信回路を示す。送信には単極性電流駆動,受信には単相信号自己同期方式を用いている<sup>(9)</sup>。送信回路では M11 はパルス電流のドライバ, M51 は常時オンとする。電流駆動のための短パルスは遅延回路で発生する。電流非駆動時は M11 をオフにしてインダクタを開放にする。図8の右側(チップ2)はクロック同期

図7 同期送受信回路 両極性電流駆動による送信回路とクロック動作作動コンパレータによる同期受信回路を用いている. SR-FF は Set Reset Flip-Flop.

図8 非同期送受信回路 単極性の電流駆動による送信回路と自己プリチャージ型の単相受信回路を用いている。 M32 のゲートバイアスを適当な値に制御している。 Tdata のバイナリーデータを P-Gen (Pulse Generator) でシングル・ダブルパルスにエンコードし, P-Dec (Pulse Decoder) でバイナリーデータに戻している。

不要な自己プリチャージによる受信回路である。M12 は常時オン、M52 は常時オフにする。 $L_2$  の上部端子の電圧は $C_1$  で直流カットしてバイアス電圧にレベルシフトする。M32 のゲート電圧はバイアス回路で適切なしきい値に設定されている。レベルシフトされた受信信号がしきい値を越えるとM32 がオンになり、ノード①を放電して0 にする。インバータ二段動作後、M42 がオンになってノード①を充電する。更に、インバータ一段遅延後、M22 をオンにして $L_2$  の受信インダクタの共振を強制的に抑圧するようにして,高速動作を可能にしている。

図8の自己タイミング方式非同期動作送受信回路の基本機能は、入力のパルスの遷移のタイミングの送受信である。電気配線と同じように使うには、"0"、"1"の状態を通信することが必要であるので、"0"をシングルパルスで、"1"をダブルパルスにエンコードする方式が提案されている<sup>(9)</sup>. 図8ではP-Genでシングル/ダブルパルス生成し、P-Decでデコードする。これにより、電気配線と同じように情報を送ることができるが、ダブルパルスを用いるので、ビットレートは約1/2になる。

# 3. インダクタ対無線インタコネクションの 実測評価

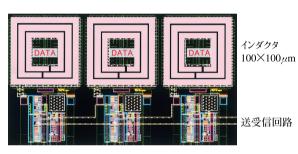

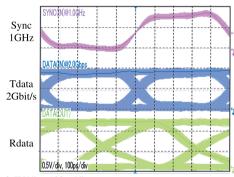

$0.18\mu m$  CMOS 技術を用いたトランシーバの 3ch 分のレイアウト例を図 9 (a) に示す。マニピュレータに試作チップをセットして対向させて,データ伝送特性を測定して,  $200\mu m$  サイズのインダクタで距離  $100\mu m$  の場合,非同期方式でビットレート 1.0Gbit/s の性能が消費電力 0.95mW で実現されている (9) 。また,ビット誤り率  $10^{-10}$ 以下が確認されている。図 9 (b) はインダク

(a) 送受信回路のレイアウト例

0.5V/div., 100ps/div.

# (b) 同期送受信回路の実測波形

図9 インダクタ対無線送受信回路の試作及び測定 (a)  $0.18\mu$ mCMOS, 五層配線技術を用いてレイアウト, インダクタは図3と同等。(b) 2Gbit/s のランダムパルスを入力したときの実測波形。 Sync は同期パルス信号であり,立ち上がり,立ち下がりの両方を用いて,ビットレートの 1/2 の周波数で送受信回路を同期動作させている。

タサイズ  $100\mu$ m, インダクタ間距離  $50\mu$ m の場合の測定値であり、非同期方式で 1Gbit/s、同期方式で 2Gbit/s 以上が達成されている.

インダクタ間距離と位置ずれの許容量を誤り率  $10^{-10}$  以下の条件で評価すると、位置ずれはインダクタサイズ

の20%程度まで許容される.

1,024ch 多重で 1Tbit/s の超高バンド幅のデータ転送が報告されている (8) .  $0.18\mu$ mCMOS を用いて,インダクタサイズ約  $30\mu$ m,チャネルピッチ  $30\mu$ m,インダクタ間距離  $15\mu$ m と小形化して,1,024ch を 1mm² に,127ch のクロック用を 1mm² に集積している。クロック周波数 1GHz,電源 1.8V のとき,消費電力は送信:2.2W,受信:0.6W,クロック:0.2W であり,1ch 当りに換算すると 3mW となり,これは数百 Mbit/s 以上の高速ディジタルインタフェース(LVDS:Low Voltage Differential Signal)の 1/10 程度である。更に,駆動電流の最適化を図って,1 ビット転送当りの消費エネルギーを 0.14pJ/bit に低減させたとの報告もある(10).

この電磁結合はデバイスのスケーリングによる性能向上が期待できる。高密度化のためのスケーリング則として、インダクタサイズと距離、MOS サイズ、電源電圧を 1/a にスケーリングして、巻き数を  $a^{0.5}$  に増やしてインダクタンス、結合係数 k を一定にするものである。これを達成できれば、転送速度が a 倍、回路の密度が $a^{\alpha}$  倍、ビット当りのエネルギーが  $1/a^{3}$  となることが予測される(11).

# 4. インダクタ対無線インタコネクトを用いた 三次元集積

多数のインダクタ対をチップ上の任意の位置に形成することで,隣接チップ間で非接触情報転送ができるので, 従来の電気接続に代る実装技術として利用できる. チッ プのパッドをインダクタに代えると, 静電破壊保護回路が不要になるので, 広帯域化が図れる. また, インダクタで結合して非接触のウェーハテストやチップテストを行うこともできる.

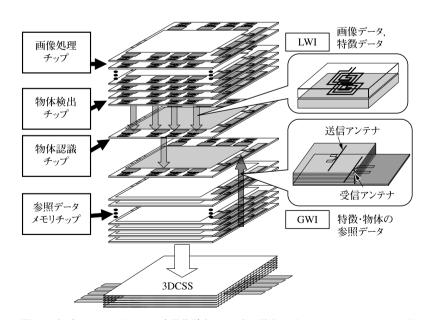

更に、インダクタ対結合は三次元集積にも適用でき、チップ上の局部に分散するデータを隣接チップに並列転送できるので、LWI (Local Wireless Interconnection)と呼ばれる。LWI のみでなく、電磁波結合の両方を用いた三次元集積システムが提案されている $^{(12)}$ . 電磁波結合はシステム全体に情報を送るのに適するので GWI (Global Wireless Interconnection)と呼ばれる。中心周波数  $3.6 \, \mathrm{GHz}$  のガウス形パルスを用いた UWB (Ultra Wideband)方式でビットレート  $1.16 \, \mathrm{Gbit/s}$  が得られている $^{(13)}$ .

無線インタコネクションを用いると,電源以外のチップ間電気接続が不要になるので,異なる機能や材料のチップを容易に集積できる.

三次元カスタムスタックシステム(3DCSS: 3D Custom Stack System)と呼ばれる構造を図 10 に示す.電源系の端子数は信号に比べて,圧倒的に少なく,大形が許容されるので,貫通ビアに比べて低コストで接続でき,熱応力の問題も解決しやすいので,高信頼化も期待されている.これらの特徴により,高性能コンピュータや画像処理システムの一層の性能向上と低コスト化の両立が期待されている(12).

3DCSS の応用として,図10 に示す高い認識性能を持ったビジョンシステムが提案されている.生体の階層的視覚処理系を模擬しており,3種のチップ,

図 10 無線インタコネクト三次元集積 (3DCSS) の構造とビジョンシステム 電磁結合 (LWI) と電磁波結合 (GWI) の両方を用いた三次元カスタムスタックシステム (3DCSS). 生体の視覚処理系を模擬しており、3種のチップ、①ピクセルアレー形画像処理チップ、②物体検出・認識チップ、③参照データメモリチップで構成され、画像データは LWI で、参照データは GWI で転送する.

- ① 差分演算回路,抵抗ネットワークで構成される二 次元ピクセルアレー形画像処理チップ

- ② 画像から顔や物体を検出・認識するチップ

- ③ 認識のための参照データのメモリチップ

の各々を複数個集積する構成である. ここで二次元画像 データには LWI を用い、メモリからブロードキャスト する参照データなどは GWI を用いる<sup>(12)</sup>. このように同 一のチップを複数個三次元集積するには、インダクタ間 距離を短くできるような薄い電源系の配線技術の開発が 課題である.

三次元集積における情報転送について述べたが,この技術は電力の転送に用いることもできる.従来,フォトカップラを用いていた高耐圧スイッチ,医療用センシングシステムで体内のカプセルに電力を送り,同時に情報も通信するなど多くの応用が展開しつつある.

## 5. ま と め

インダクタ対結合によるチップ間無線インタコネクション技術により、同期方式では、ビットレート 2Gbit/sが消費電力 2mW で実現され、1Gbit/sのインダクタ対を1,024ch 並列化して全バンド幅1Tbit/sが消費電力3Wで実現されている.一方、非同期方式ではビットレート1Gbit/sが1mW という低消費電力で実現されている.これらは有線のインタコネクションに比較して10倍の電力効率である.これら技術を三次元集積システムに導入することにより情報処理能力の飛躍的な向上が期待できる.

## 文 献

- (1) J.U. Knickerbocker, C.S. Patel, P.S. Andry, C.K. Tsang, L.P. Buchwalter, E.J. Sprogis, H. Gan, R.R. Horton, R.J. Polastre, S.L. Wright, and J.M. Cotte, "3-D silicon integration and silicon packaging technology using silicon through-vias," IEEE J. Solid-State Circuits, vol.41, no.8, pp.1718-1725, 2006.

- (2) M. Koyanagi, Y. Nakagawa, K.W. Lee, T. Nakamura, Y. Yamada, K. Inamura, K.T. Park, and H. Kurino, "Neuromorphic vision chip fabricated using three-dimensional integration technology," ISSCC Digest of Tech. Papers, no.17.2, pp.280-271, 2001.

- (3) K. Kanda, D.D. Antono, K. Ishida, H. Kawaguchi, T. Kuroda, and T. Sakurai, "1.27Gb/s/ch 3mW/pin wireless superconnect (WSC) interface scheme," ISSCC Digest of Tech. Papers, no.10.7, pp.186-187, 2003.

- (4) D. Mizoguchi, Y.B. Yusof, N. Miura, T. Sakurai, and T. Kuroda, "A 1.2Gb/s/pin wireless superconnect base on inductive inter-chip signaling (IIS)," ISSCC Digest of Tech. Papers, no.7.6, pp.142-143, 2004.

- (5) T. Kikkawa, K. kimoto, and S. Watanabe, "Ultra wideband characteristics of fractal dipole antennas integrated on Si for ULSI wireless interconnects," IEEE Electron Device Lett., vol.26, issue 10, pp.767-769, 2005.

- (6) S.S. Mohan, M.M. Hershenson, S.P. Boyd, and T.H. Lee, "Simple accurate expressions for planar spiral inductances," IEEE J. Solid-State Circuits, vol.34, no.10, pp.1419-1424, 1999.

- (7) N. Miura, D. Mizoguchi, M. Inoue, H. Tsuji, T. Sakurai, and T. Kuroda, "A 195Gb/s 1.2W 3D-stacked inductive inter-chip wireless superconnect with transmit power control scheme," ISSCC Dig. of Tech. paper, no.14.5, pp.264-265, 2005.

- (8) N. Miura, D. Mizoguchi, M. Inoue, K. Niitsu, Y. Nakagawa, M. Tago, M. Fukaishi, T. Sakurai, and T. Kuroda, "A 1Tb/s 3W inductive-coupling transceiver for inter-chip clock and data link," ISSCC Dig. of Tech. paper, no.23.4, pp.424-425, 2006.

- (9) M. Sasaki and A. Iwata, "A 0.95mW/1.0Gbps spiral-inductor based wireless chip-interconnection with asynchronous communication scheme," Symposium on VLSI Circuits, no.22.3, pp.348-351, 2005.

- (10) N. Miura, H. Ishikuro, T. Sakurai, and T. Kuroda, "A 0.14pJ/b inductive-coupling inter-chip data transceiver with digitally-controlled precise pulse shaping," ISSCC Dig. of Tech. paper, no.20.2, pp.358-359, 2007.

- (11) 黒田忠広, "チップ間を 1T ビット/秒で伝送できる無線通信技術を開発," 日経エレクトロニクス, 2006.3.13 号, pp.137-148, 2006

- (12) A. Iwata, M. Sasaki, T. Kikkawa, S. kameda, H. Ando, K. Kimoto, D. Arizono, and H. Sunami, "A 3D integration scheme utilizing wireless interconnections for implementing hyper brains," ISSCC Dig. of Tech. Papers, no.14.4, pp.262-263, 2005.

- (13) P.K. Saha, N. Sasaki, and T. Kikkawa, "A single-chip gaussian monocycle pulse transmitter using 0.18µm CMOS technology for intra/inter chip UWB communication," Symp. on VLSI Circuits, pp.252-253, 2006.

$(平成 \, 19 \, \mp \, 5 \, \, \hbox{$\it |$|} \, \, 7 \, \, \hbox{$\it |$|} \, \,$

岩田穆(正員:フェロー)

昭 43 名大・工・電子卒、昭 45 同大学院修士課程了。同年電電公社(現 NTT)通信研究所入社、通信用アナログ集積回路の研究開発に従事。平7広島大教授、平7,8 年度本会集積回路研究専門委員長、著書「VLSI工学一基礎・設計編一」(本会編)、平6全国発明表彰特許庁長官賞、平19 IEEE Trans. on Circuits and Systems Darlington Best Paper Award 各受賞、工博、